摘要: 本文针对当前人工智能发展中的一些关键技术,介绍CPU+GPU主流计算模式的高算力与高功耗的现状、AI芯片的发展以及新型计算架构的创新。

本文提出了算存算一体计算理论、方法;提出了算存算一体计算平台以及邻域存储体有效带宽、AI系统有效算力的计算方法。介绍了算存算一体计算理论的应用。

图源:豆包AI

01 前言

AI的发展包括AI算法、AI硬件、AI系统的发展。在AI发展的大潮中,涌现出了一些新型的计算架构。这些新型计算架构包括存算一体、感存算一体、算存算一体计算架构。这些新型计算架构在解决内存墙问题、提升算法算力、降低功耗等方面发挥了出色的作用。

02 CPU+GPU主流计算模式

Nvidia公司GPU板卡的发展经历了从计算机显卡到通用处理器的发展历程。1999年,Nvidia推出了如图2.1所示的世界上第一个GeForce 256 型GPU。

图.2.1 GeForce 256 型GPU

Nvidia公司的GPU板卡发展迅猛,应用广泛,形成了CPU+GPU的计算模式。

在《MIT科技评论》十大突破性技术中,深度学习是2013年十大突破性技术。深度学习人脸识别采用CPU+GPU计算模式,将人脸识别率提高到99%以上,推动了我国乃至全球人脸识别的大规模应用。中国天河一号超算计算机应用了7168块 GPU,算力全球夺冠。

Nvidia公司的GPU板卡在存储体带宽方面,2010年11月发布的GeForce GTX580型板卡,其存储体带宽为192GB/s。2020年10月发布了RTX A6000型板卡,其存储体带宽为768GB/s。2022年发布了H100型GPU板卡,其存储体带宽为7.8T/s。10年间,RTX A6000型板卡比GeForce GTX580板卡的存储体带宽提高了4倍。2020年到2022年仅2年的时间,H100型板卡比RTX A6000 型板卡的存储体带宽竟然提高了超10倍。凸显出Nvidia公司对存储体带宽的追求。

Nvidia公司的GPU板卡在算力方面,GeForce GTX580型板卡算力:1.6TFLOPS,RTX A6000型板卡算力:38.7TFLOPS,H100 NVL型板卡算力:134TFLOPS。10年间,RTX A6000型板卡比GeForce GTX580板卡的算力提升了24.1875倍。2020年到2022年的2年时间,H100型板卡比RTX A6000 型板卡的算力仅提升了约3.46倍。

2020年到2022年的2年间,H100与A6000的比较,H100的存储体带宽提升超10倍,算力仅提升约3.46倍。其原因值得探讨。

Nvidia公司的GPU板卡在功耗方面,GeForce GTX580型功耗:功耗240瓦;RTX A6000型板卡功耗:300瓦;H100 NVL型板卡功耗:700瓦。功耗的飙升真是步步高,高到惊人的程度。

Nvidia公司GPU板卡的发展,现在是否已进入到天花板状态,值得探讨。

03 CPU+GPU计算模式面临的挑战

GPU大算力伴随的高功耗引发了业界的深深担忧,低功耗替代方案已成为业界的探索方向。在《MIT科技评论》十大突破性技术中,微型人工智能是2020年十大突破性技术。2020年左右,微型人工智能强力兴起,AI芯片发展迅猛。

TPU 由谷歌率先推出。为了适应在智能时代的发展,谷歌做出改变,停止在服务器规模上的无限扩张。

2013 年,谷歌研发成功首款TPU板卡,这也是全球首款TPU板卡,用于AI计算。谷歌的AlphaGo内置40片TPU芯片,支持12层神经网络的复杂计算。在人机大赛中战胜了著名棋手李世石,展示了AI芯片的非凡能力。2017 年,谷歌相继推出了Cloud TPU,用于云端计算。与GPU相比,TPU在每瓦特的算力上具有一定优势。

中科院计算所的寒武纪芯片是国内的早期的AI芯片。中科院计算所的陈云霁、陈天石等人在2014年3月召开的国际顶级学术会议ASPLOS上发表了《DianNao:一种小尺度的高吞吐率机器学习加速器》论文并获得了最佳论文奖。2014年12月,陈云霁、陈天石等人在国际顶级学术会议MICRO上发表了《DaDianNao:一种机器学习超级计算机》论文并获得了最佳论文奖。这两篇论文在国际上产生了非凡的影响。

中科寒武纪科技股份有限公司于2021年11月推出的思元370人工智能芯片,该芯片是寒武纪首款采用chiplet(芯粒)技术的AI芯片,采用7nm工艺,算力为256TOPS(INT8)。

华为公司于2017年9月2日在德国IFA2017(柏林国际电子消费品展览会)上,发布人工智能手机芯片麒麟970,算力达到1.92TOPS。

华为公司于2019年8月23日推出AI处理器:昇腾910AI芯片采用7nm工艺。该处理器算力:16bit精度,256TOPS;8bit精度: 512TOPS。

华为公司于2019年9月30日发布Atlas 300 AI加速卡软件开发指导书(型号3000)。

Atlas 300 AI加速卡(型号 3010)采用4个昇腾310芯片。每个昇腾310芯片连接8个LPDDR4X存储芯片(单个存储芯片的存储容量为1GB,存储芯片的读写频率为3200Mbps),4个昇腾310连接32个存储芯片,总的存储容量为32GB,总的存储体带宽为204.8GB/s。Atlas 300 AI加速卡的存储体带宽为204.8GB/s。算力:64 TOPS INT8;32TFLOPS/FP16。功耗为67W。

功耗指标以及算力/每瓦特指标已成为当前的对GPU的挑战性指标。无论是谷歌公司机器学习的TPU芯片,还是华为公司的昇腾910芯片,以及寒武纪思元100芯片,都在算力/每瓦特的指标上取得了优秀性能,并在算力上追赶NVIDIA的GPU。CPU + GPU主流计算模式面临着强大挑战。

计算架构的创新

4.1 冯诺依曼架构

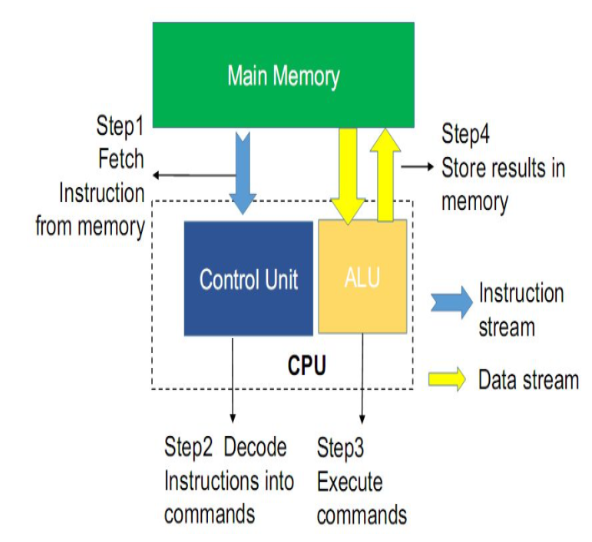

1981年是一个值得记忆的年份,这一年美国IBM公司推出了IBM PC微机,由此开始了一个微机发展、微机应用的PC时代。PC/XT(8088/8086)、286、386、486、586等系列微机,DOS、OS/2、WINDOWS、WINDOWS NT、WINDOW 95等微机操作系统,ISA、MCA、EISA、VESA、PCI、AGP系列微机总线,微机的众多技术日新月异的迅猛发展,呈现出一派欣欣向荣的景象。在微机发展中,逐渐形成了冯诺依曼架构。可以说,冯诺依曼架构是计算技术发展的一个里程碑。冯诺依曼架构的结构示意图如图4.1所示。

图4.1 冯诺依曼架构的结构示意图

冯诺依曼架构包含存储单元、控制单元和计算单元。计算机进行运算,需先把数据存入主存储体,再按顺序从主存储体中取出指令一条一条的执行。访问主存储体的速度直接影响计算速度。

计算机通常采取高速缓存(SRAM)、内存(DRAM)、磁盘的三种存储方式。在早期的数据存储技术中,既有磁带、磁盘,还有闪存、内存。数据库奠基人Jim Gray曾说:磁带已经死了,磁盘已经落伍,闪存成为存储,内存才是王道。计算机直接存取内存的数据进行计算,可称为基于内存的计算。计算机直接存取硬盘的数据进行计算,可称为基于硬盘的计算。在计算机的数据访问中,曾经记录的一组数据是:单次读取磁盘数据为5ms,单次读取内存数据为5ns,访问内存比访问磁盘快100万倍。显然,读取内存数据的速度远远高于读取磁盘数据的速度,读取内存数据实现了更快的数据传输。

处理器算力快速提升,而计算机内存的访问速度却提升缓慢。这使得处理器的处理速度远远快于内存的读取速度,直接导致了“存储墙”的出现,严重拖慢了计算机的运行速度。

“存储墙”问题不仅局限于计算机,还影响众多领域。图像存储体也存在同样问题。

清华大学研制成功的“TS-79小型通用数字图像图形处理系统”于1982年1月18日通过国家电子计算机工业总局鉴定,1983年获北京市科学技术成果二等奖。笔者曾参与该系统的研制,并于1983年发表了笔者的第一篇学术论文“物体的边界跟踪与周长面积的确定”。该论文的研究工作是在“TS-79小型通用数字图像图形处理系统”中完成的。将一帧图像存入图像存储体,对该帧图像进行邻域计算。存储体的一个读周期只能读一个图像数据,9个读才能从存储体读出3x3的图像数据,计算机再进行计算。编程麻烦,处理速度慢。其根源还是内存墙问题。这些问题启发笔者走上了邻域存储体的研究方向。

4.2 存算一体计算

处理器性能大幅度提升,而存储体性能的提升缓慢。不均衡的发展速度造成了存储体数据存取速度严重滞后于处理器的计算速度。更为突出的是,随着人工智能的发展,面对计算中心大数据流的数据存取需求,内存墙问题则成为加速计算的关键瓶颈。

在传统计算机的设定里,存储模块是为计算服务的,因此设计上会考虑存储与计算的分离与优先级。如今,存储和计算不得不整体考虑,以最佳的配合方式为数据采集、存储、传输和处理服务。

计算技术的迅猛发展,促进了存算一体计算架构的发展。

存算一体计算(Computing in Memory)是将计算嵌入存储器中的计算。其特点是以新的架构进行包含数据存储的运算。

存算一体芯片将存储和计算功能融为一体。其优越性在于它能够减少数据传输的延迟,有效的克服了内存墙弊端,大幅度提高了计算速度。

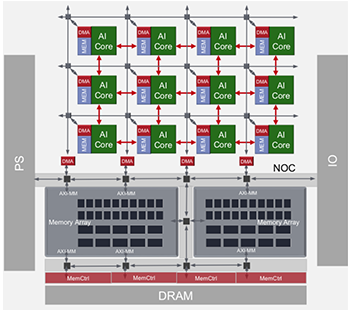

赛灵思公司历时4年,动用了1500名工程师,投入超过10亿美元,于2018年建成自适应计算加速平台,这是一个高度集成的多核异构计算平台,改善了冯伊曼内存墙,优化了数据搬运路线,实现了存算一体计算。图4.2给出了赛灵思公司多核异构的AI芯片结构图

图4.2 赛灵思公司多核异构的AI芯片结构图

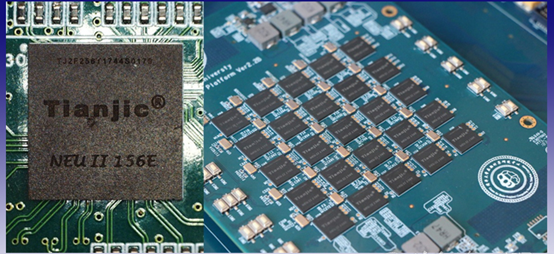

清华大学研制成功“天机芯”类脑计算芯片,该芯片是面向人工通用智能的世界首款异构融合类脑计算芯片。基于此研究成果的论文“面向人工通用智能的异构天机芯片架构”(Towards artificial general intelligence with hybrid Tianjic chip architecture)发表在2019年8月1日的顶刊Nature上。Nature并将该芯片的图示登在其杂志的封面上。“天机芯”芯片采用28nm工艺制造。采用28nm制造工艺的AI芯片达到世界级水平的成果足以说明了体系架构的重要性。

图4.3给出了Nature登在封面的“天机芯”图示

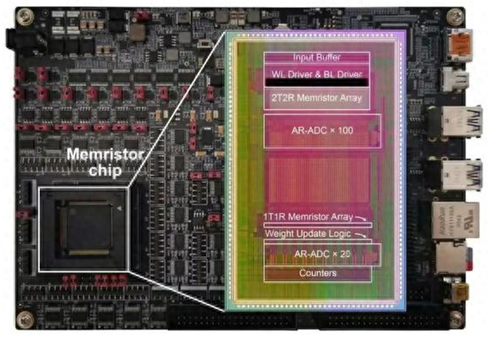

清华大学研制成功忆阻器存算一体芯片,该研究成果已发表在顶刊Science上。该芯片包含支持完整片上学习所必需的电路模块,成功完成图像分类、语音识别和控制任务等多种片上增量学习功能验证,展示出高适应性、高能效、高通用性、高准确率等特点,有效强化智能设备在实际应用场景下的学习适应能力。

图4.4为忆阻器存算一体芯片

清华大学集成电路学院发布国际首款面向视觉AI大模型的三维DRAM存算一体架构,解决存储墙瓶颈,提高AI大模型计算效率。

中科院微电子所也发布基于外积运算的数模混合存算一体宏芯片,展示出高效能的优势。

存算一体计算架构的应用目前正在向多方向发展。

4.3 感存算一体计算

感存算一体计算是将感知、存储和计算融为一体的计算,由此形成了一种新的计算架构。

在冯诺依曼架构中,感知、存储、计算是分离的,而感存算一体计算是将感知、存储、计算有机的结合在一起,实现了高效计算。

“感知”通指数据的采集和数据的传输,包括传感器技术和数据通信技术;“存储”通指数据的存储和数据的管理,既包括存储体技术,也包括云计算和物联网等技术。“计算”通指数据的处理和分析,包括人工智能等技术。

清华大学集成电路学院、信息国家研究中心研究团队研制了具有多模态的感存算一体化光电忆阻器阵列,搭建了单片集成的感内计算原型系统,用于处理视觉任务的处理。

九天睿芯首款视觉应用的感存算一体新型架构计算芯片ADA20X

于2021年5月流片成功。该芯片具有高度可定制性,可以依据不同的需求,定制不同的专用芯片。其算力覆盖从0.3Tops-200Tops,可以满足平板电脑、可穿戴、智能家居、AR/VR、电池供电IPC、ADAS等多种不同应用场景。

ADA20X可同时支持基于帧的相机和事件相机的处理。图4.5给出了ADA20X板卡外形图。

图4.5 ADA20X板卡

4.4 算存算一体计算

算存算一体计算是将算法、存储和处理融为一体的计算。其计算平台由计算机、存储体、计算芯片构成。计算芯片包括AI芯片、FPGA等芯片。

清华大学电子工程系早期研发成功图像处理系统和图像板卡,为研究算存算一体计算奠定了坚实的基础。这些系统和板卡包括:

1982年1月研制成功TS-79小型通用数字图像图形处理系统,1983年获北京市科学技术成果二等奖。

1985年9月研制研制成功TS-84微机图像图形处理系统, 1988年获教育部科技进步二等奖。

1990年制成功QH905图像卡。

1991年研制成功TH-915图像卡。

1991年研制成功TH-915F高速图像卡

1992年研制成功TH-925图像卡。

1992年研制成功TH-925C彩色图像卡。

2004年研制成功TH-2004图像卡。

2005年研制成功双TMS320C6201人脸检测卡。

算存算一体计算的研究历程包括:

(1)线跟踪算法及其硬件实现。1991年6月-1993年6月清华基金项目。

(2)1992年研制成功二值图象邻域处理机。

(3)1997年研制成功NIPC-1型邻域图像并行计算机。

(4)1999年研制成功NIPC-2型邻域图像并行计算机。

(5)2008年研制成功NIPC-3型邻域图像并行计算机,这是2006年国家自然科学基金项目。

(6)2019年研制成功NIPC-4型邻域图像并行计算机。

(7)2022年完成NIPC-5型邻域图像并行计算机。

(8)2024年研制成功NIPC-6型邻域图像并行计算机。

从研发通用图像板块,到专注研究邻域图像并行计算机;从应用高速处理芯片实现高速图像处理的科研方向。转换到研究邻域存储体、构建算存算一体计算平台的科研方向。这是一条成功的路。1999年2月我们在电子学报杂志上发表了“邻域图像帧存储体的理论及其实现”论文,前瞻性的指出了邻域存储体在推倒内存墙的积极作用。

算存算一体计算理论及其应用

5.1 算存算一体计算理论

算存算一体计算理论由两部分组成。

(1)邻域存储体理论。

(2)邻域存储体、计算器件和计算机一体的计算平台。

其中,计算器件包括FPGA、AI芯片等计算器件。

邻域存储体理论,其在应用上实现了存储体的多数据并行存取,解决了内存墙问题。

邻域存储体、计算器件和计算机一体计算的计算平台,实现了存储体的多数据并行存取、硬件处理器的并行处理和计算机处理相结合的高速计算。

算存算一体计算理论初建于2008年,并逐渐发展至今。

5.2 邻域存储体理论

邻域存储体理论由一维存储芯片堆叠和一维存储芯片数据bit位分段裂变的不完全轮换矩阵理论以及二维存储芯片堆叠和二维存储芯片数据bit位分段裂变的不完全轮换矩阵理论构成。

5.2.1 存储芯片二维堆叠

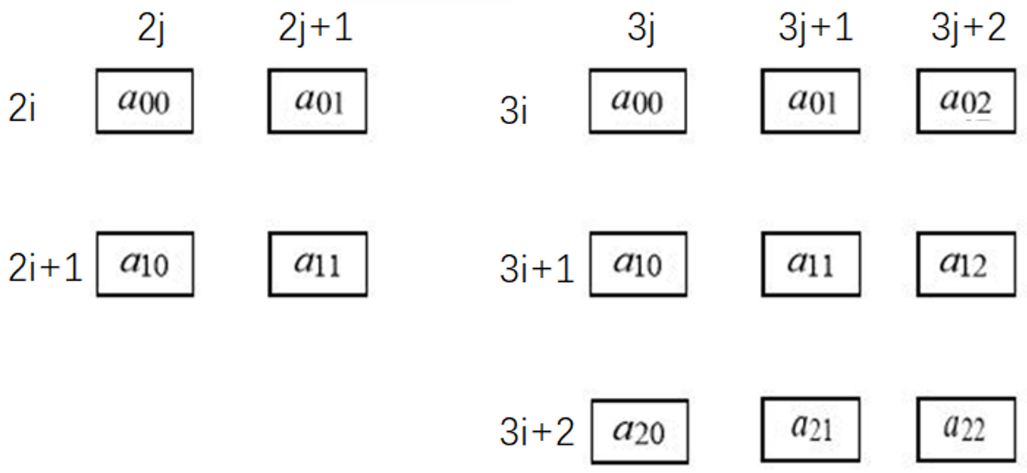

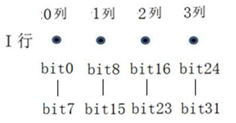

图5.1给出了存储芯片二维堆叠实例。

图5.1 存储芯片二维堆叠实例

左图:4个存储芯片2x2堆叠 右图:9个存储芯片3x3堆叠

图5.1左图是2x2的存储芯片堆叠,可以实现2x2邻域图像数据的并行存取。其数据存储规律为:2i行0列的8bit图像数据存储在a00芯片,2i行1列的8bit图像数据存储a01芯片;2i行2列的8bit图像数据存储在a00芯片,此时a00芯片的列地址加1。2i行3列的8bit图像数据存储在a00芯片,此时a01芯片的列地址加1。以此为例,实现了2x2的存储芯片堆叠的图像数据并行存取

图5.1右图是3x3的存储芯片堆叠,可以实现3x3邻域图像数据的并行存取。

如果要实现4x4的存储芯片堆叠,按上述方法,则需要16个存储芯片,其难度非常大。为解决二维大邻域数据的并行存取难题,我们提出了二维存储芯片堆叠和二维存储芯片数据bit位分段裂变的不完全轮换矩阵理论。

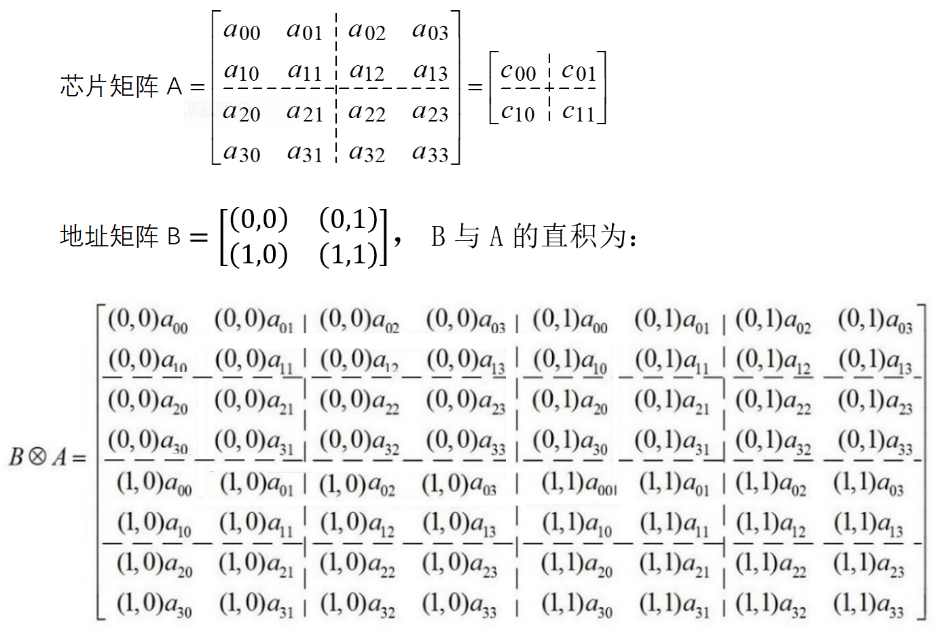

以4x4邻域并行存取为例。芯片矩阵A中有a00等16个按照4x4排列的存储芯片,虚线划分为四块,由c00等4个芯片分别替代对应的四个芯片。地址矩阵B给出了c00等4个芯片的对应地址。

式5.1中的矩阵B

A表明, C00、C01、C10、C11存储芯片的堆叠可以替代16个存储芯片,由此实现了4x4邻域数据的并行存取。

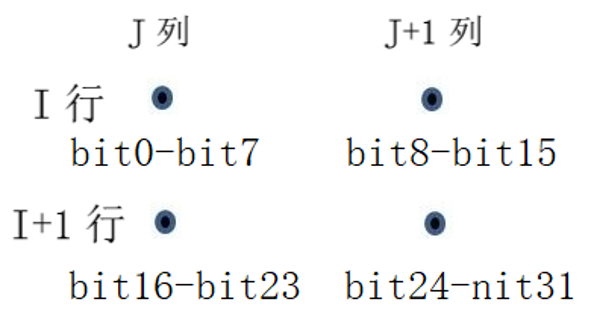

图5.2给出了一个存储芯片数据bit位二维裂变的实例。

图5.2 32bit字长裂变为4个8bit的相邻数据

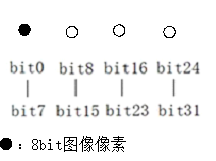

图5.2中,图像像素的数据位为8bit,存储芯片的数据bit位为32bit。将32bit裂变为4个8bit,按照图5.2所示的排列可实现2x2邻域图像数据的并行存取。

5.2.2 存储芯片一维堆叠

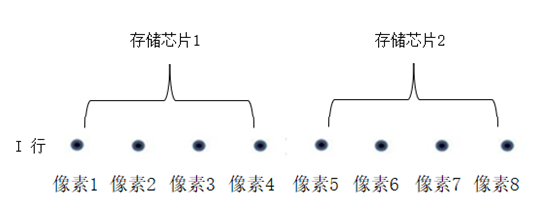

图像像素的数据位为8bit,每个存储芯片数据bit位为32位,如果以水平方向进行一维存储芯片数据bit位的分段裂变,则1个存储芯片的数据bit位可以存储4个8bit的图像像素。图5.3给出了单个存储芯片水平方向分段裂变的示意图。

图5.3 单个存储芯片水平方向分段裂变的示意图

图5.4给出了2个存储芯片水平方向分段裂变的示意图。

图5.4 2个存储芯片水平方向分段裂变的示意图

图5.4中,两个存储芯片均按照图5.1所示的数据位分段裂变,再进行排列,则可以在存储体的一次读或写操作中,就可以实现读或写I行的8个图像像素。

多个同类型的存储芯片采用图5.4所示的在水平方向进行分段裂变,则可以在存储体的一次读或写操作中,可以实现读或写I行的更多个图像像素。

按照图5.4的结构方式构建的存储体,称为行邻域存储体。行邻域存储体的结构图如图5.5所示。

图5.5 行邻域存储体的结构图

选择N个同型号存储芯片(N≥2且N≤16),其存储芯片的数据bit位大于或等于16bit、32bit、64bit、128bit。并将N个存储芯片按照水平方向堆叠,来构成行邻域图像存储体。行邻域图像存储体的每个存储芯片的地址位、时序位一一对应的连接在一起,而数据位则各自独立。

式5.1给出了存储体带宽的数学表达式。

C = N * k1 * ƒ0/8bit (5.2)

式5.1中:N:水平方向堆叠的存储芯片数量

k: 单个存储芯片数据bit位的位数

ƒ0: 存储体读写时钟频率

某存储体1个地址的32bit数据位只存储一个8bit的图像像素(如图5.6所示),其余24个bit位空置,存储体的利用效率不高。由此,我们提出了存储体有效带宽定义。

图5.6 存储体利用效率不高的实例

定义5.1:

存储体有效带宽等于存储体有效位宽和存储体读写频率数的乘积。

存储体有效带宽E的数学表达式为:

E = N * k2 * ƒ0/8bit (5.3)

式5.3中,N:构成行邻域存储体的存储芯片数量

k2: 单个存储体芯片数据位的有效bit位数

ƒ0: 存储体读写时钟频率

如单个存储体芯片数据位为32bit,而图像数据位为8bit,则存储体有效带宽E只是存储体带宽C的四分之一。

实现了存储体高有效带宽,推倒了内存墙这,正是邻域存储体的独特作用。

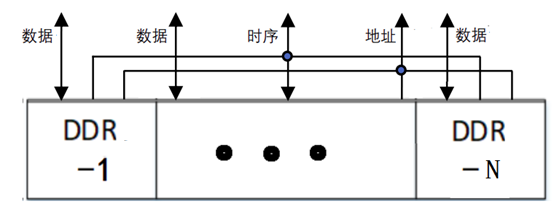

5.3 算存算一体计算平台

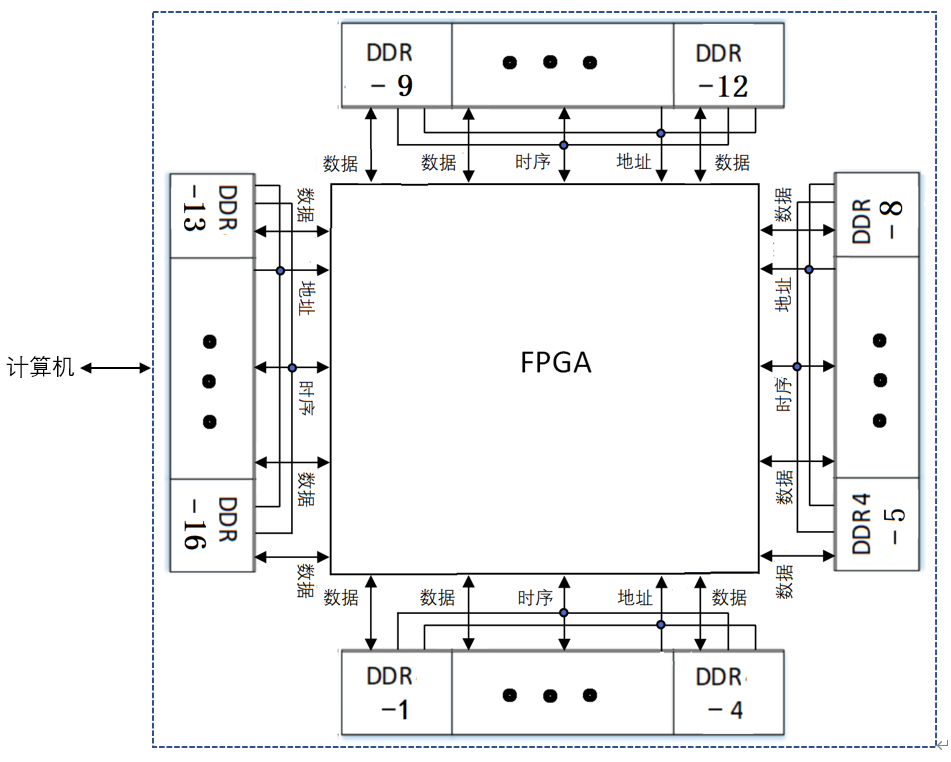

应用邻域存储体高有效带宽的能力,再辅以高速计算,形成一种使用现有成熟器件的存算一体计算。再辅以计算机的丰富资源,由此构建成算存算一体的计算平台。图5.7给出了算存算计算平台的结构图。

图5.7 算存算一体计算平台的结构图

图5.7中,虚线框内包括NIPC-6型邻域图像并行计算板卡的核心结构。计算芯片采用了通用的FPGA芯片,当然也可以采用其他的AI芯片。所设立的4组行邻域存储体,每组行邻域存储体由4个DDR存储芯片构成,采用了图5.5所示的行邻域存储体的结构。该板卡插入通用计算机的PCI槽中。行邻域存储体、FPGA处理器、通用计算机构成一个算存算一体计算平台。

5.4 算存算一体计算的平面、立体数据处理

图5.8给出了算存算一体计算的平面数据处理示意图。

图5.8 算存算一体计算的平面数据处理示意图

图5.8所示的是采用算存算计算平台对一幅W*H的图像进行3x3卷积的示意图。

首先采用连读的形式,从行邻域存储体读出一行W个图像数据,继而在一个处理周期里,完成一行W个图像数据的3x3卷积。在H个处理周期里,采用流水线处理技术,并行完成一幅W*H图像的3x3卷积。显然,这种处理是高效的。

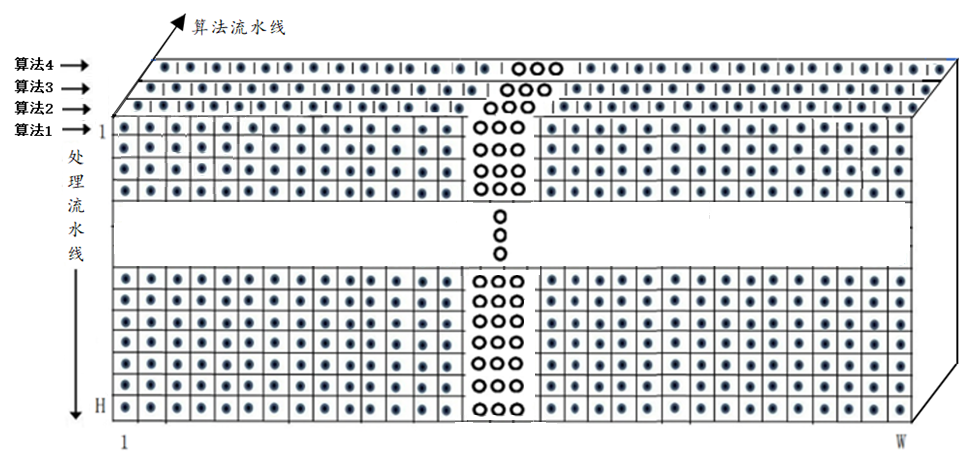

图5.9给出了算存算一体计算的立体数据处理示意图。

图5.9 算存算一体计算的立体数据处理示意图

在AI算法的应用中,有许多多层卷积级联的算法。采用图5.9所示的算存算一体立体数据处理方法,可以在H个处理周期里,采用算法流水线和处理流水线相结合的双流水线处理技术,实现4个算法的并行处理。所耗用的时间,等同于单算法的处理时间。

图5.9所示的立体数据处理方法,将具有广泛应用的潜力。在后续章节中,将有实践的一些数据佐证。

5.5 算存算一体计算实例

在前面章节中列出的NIPC系列板卡中,这里列出部分NIPC板卡的计算实例。

5.5.1 NIPC-3邻域图像并行计算机

2006年9月21日清华大学承担了国家自然科学基金项目“大邻域图像并行处理机的研究”。2008年1月18日,所研制成功“NIPC-3邻域图像并行计算机”通过了教育部的科技成果鉴定,图像处理速度达到了国际最好水平,这是一项原始性创新,在图像科学上具有重要意义。科技日报1月20日在头版进行了报道。图5.10给出了NIPC-3板卡图。

图5.10 NIPC-3板卡图

NIPC-3板卡插入通用计算机的PCI槽中。摄像机输入的视频图像经NIPC-3板卡处理后,将处理结果通过PCI总线送人计算机。对一幅512x512的视频图像进行Sobel处理,耗时仅0.11ms,优于NVIDIA的GeForce GTX 760 GPU板卡块。

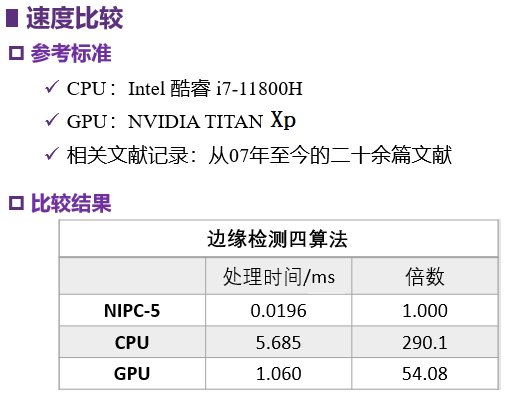

5.5.2 NIPC-5邻域图像并行计算机

我们于2022年研制成功NIPC-5邻域图像并行计算机。图5.11给出了NIPC-5板卡图。NIPC-5是一块独立的板卡,通过网络与计算机联结,构成一个算存算一体计算平台。图5.11给出了NIPC-5板卡的外观图。

图5.11 NIPC-5板卡的外观图

NIPC-5板卡采用图5.9所示的算存算一体计算的立体数据处理方法,对视频图像进行四算法处理,取得了如下的性能指标:

四算法包括高斯滤波、sobel、中值滤波、二值化处理。

显著的技术进步源于不断的追求。

5.5.3 NIPC-6邻域图像并行计算机

我们于2024年研制成功NIPC-6邻域图像并行计算机。NIPC-6板卡插入通用计算机的PCI槽中,与计算机一起构成一个算存算一体计算平台。图5.11给出了NIPC-5板卡图。NIPC-5是一块独立的板卡,通过网络与计算机联结,构成一个算存算一体计算平台。图5.12给出了NIPC-6板卡的外观图。

图5.12 NIPC-6板卡的外观图

NIPC-6邻域图像并行计算机实现了6400万/秒的人脸特征比对,功耗则小于20瓦。我们目前尚未查到有高于上述指标的公开报道。

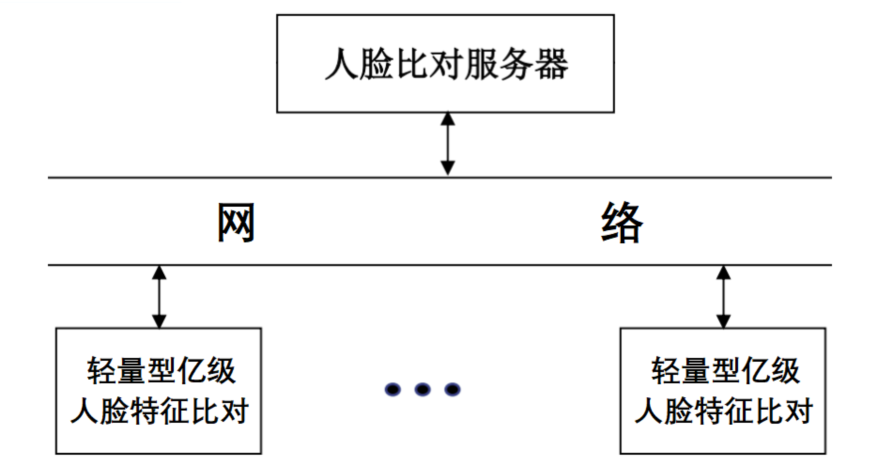

海量人脸特征比对,由于计算量大,应用中大量采用GPU板卡来完成海量人脸特征比对的高算力计算。鉴于GPU板卡的高价位、高功耗、高占地面积等问题,我们实现了GPU低功耗的替代方案。

采用两块NIPC-6邻域图像并行计算机,可以实现轻量型亿级人脸特征比对,再采用图5.13所示的集群计算的海量人脸特征比对,实现了广域的海量人脸特征比对。这种新型的海量人脸特征比对的计算架构,将展现出新型人脸特征比对的应用前景。

图5.13 集群计算的海量人脸特征比对

结束语

算存算一体计算的发展是值得期待的。NIPC-6板卡在存储芯片的使用上,仅仅应用了DDR4存储芯片。后续的研究将采用目前更高性能的存储芯片,用以扩展邻域存储体的有效带宽,进而提升有效算力。显然,这是目前提升算存算一体计算的重要发展方向。

积极开展算存算一体计算的广泛应用,包括视频图像的目标检测、跟踪方面的应用。

在已有的算存算一体计算平台上,加快进行在YOLO、Transformer、大模型方面的应用研究。

我们期待算存算一体计算的新发展。

感谢对算存算一体计算作出贡献的所有人

芯片市场规模将破1.5万亿美元!AI引爆全球半导体产业黄金十年

芯片市场规模将破1.5万亿美元!AI引爆全球半导体产业黄金十年 海康威视水下立体视觉摄像机助力智慧养殖

海康威视水下立体视觉摄像机助力智慧养殖 今日AI前沿:三月下旬三大热搜炸场,行业格局一夜变天

今日AI前沿:三月下旬三大热搜炸场,行业格局一夜变天

精彩评论